Synopsys, AI 칩 설계 시대를 열다

Hot Chips는 매년 8월 실리콘 밸리에서 열리는 기술 심포지움입니다. IEEE와 ACM SIGARCH가 후원하는 세계적인 행사입니다. 주요 주제는 마이크로프로세서와 집적회로이고, 1989년에 시작되어 올해 33번째로 개최되었습니다. Hot Chips에서는 인텔, TSMC, 삼성 등의 세계 최고의 IT/하드웨어 회사들이 최신 제품과 기술을 발표합니다. 일례로 저희 회사에서는 2016년도에 GDDR6를 Hot Chips에서 발표하기도 하였습니다. 올해도 아주 흥미로운 신제품들과 최신기술들이 소개되었습니다.

코로나 여파로 행사는 온라인으로 진행되었습니다. 발표는 녹화 영상으로, Q&A 세션은 Hot Chips 전용 Slack 채널을 통해 생방송으로 진행되었습니다. 참석자들이 많은 질의와 토론을 주고 받았습니다. 행사는 총 3일간 진행되었는데, 첫째 날에는 튜토리얼, 둘째와 셋째 날에는 8개의 컨퍼런스 발표와 3개의 키노트가 있었습니다.

그 중에서도 Synopsys의 창립자이자 CEO인 Aart de Geus 박사의 키노트는 많은 참가자들로부터 극찬을 받았습니다. Aart CEO는 인공지능을 도입한 새로운 칩 설계 최적화 솔루션인 DSO.ai (Design Space Optimization.ai)를 발표하였습니다. DSO.ai는 단 몇 주 만에 인간 전문가가 몇 달에 걸쳐 최적화한 칩보다 전력소모를 25.6% 줄인 칩을 설계해냈습니다. DSO.ai는 이미 삼성전자 LSI 사업부에 도입되어 새로운 엑시노스 칩생산에 사용된다고 합니다. 본 글에서는 칩 설계의 과정을 간략히 설명하고, Synopsis가 어떻게 이 과정에 AI를 도입하여 성과를 낼 수 있었는지에 대해 설명합니다.

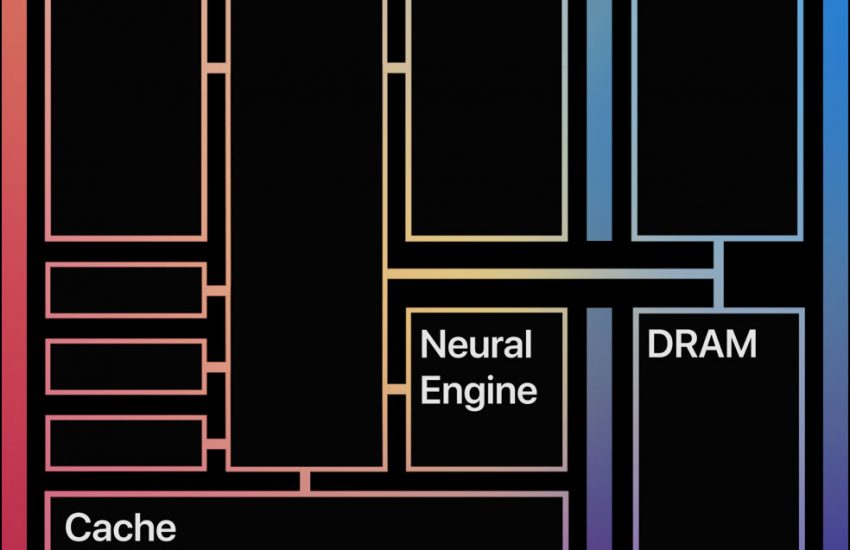

본격적인 DSO.ai 설명에 앞서 Synopsys와 칩 설계 과정을 간단히 알아보겠습니다. Synopsys는 실리콘 프로세서의 설계 및 검증을 위한 설계 자동화 (EDA, Electronic Design Automation) 솔루션을 판매하는 미국의 기업입니다. 대중들에게는 생소하지만, S&P500에도 속해 있는 명실상부 EDA분야 최고의 회사입니다. Synopsys의 솔루션은 고 레벨 하드웨어 설계, Logic 합성(Synthesis), Behavioral 합성, Place and Route, 타이밍 분석, 물리적 트랜지스터 레벨 회로 시뮬레이션까지 대부분의 칩 개발프로세스를 자동화 합니다. 이를 통해 칩 개발자가 많은 시간과 노력을 절감할 수 있게 합니다.

그럼에도 불구하고 칩 설계 프로세스에는 여전히 많은 시간과 비용이 필요했습니다. 기존의 칩 설계 프로세스는 다음과 같습니다. 첫째, HDL (Hardware Description Language)를 사용해 추상적 하드웨어 기능(Function)을 기술합니다. 둘째, 이 HDL을 Synopsys의 Design Compiler를 사용해 전자 회로 레벨로 합성합니다. 셋째, 합성한 회로가 성능, 소모 전력, 면적 요구사항 등의 설계 목표를 만족하는지 확인합니다(같은 기능을 수행하는 회로들도 게이트와 연결 선의 수가 달라 성능, 소모 전력, 면적이 다를 수 있습니다). 합성한 회로가 설계 목표를 만족한다면 결과물을 반도체 제조 회사(예: TSMC)에 의뢰하여 실제 칩으로 제작 후 검증합니다. 모든 단계에서 설계 목표가 만족될 때까지 전문가들은 파라미터, HDL, 설계목표 등을 수정하여 반복적으로 재설계를 수행합니다. 이러한 반복 작업은 약 수개월에 걸쳐 진행되며, 많은 노력과 비용을 필요로합니다.

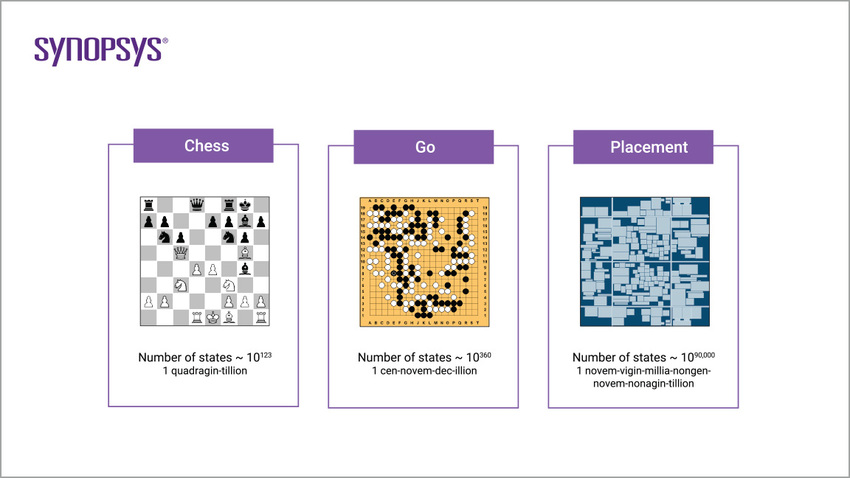

Synopsys는 이 문제를 바둑과 같이 바라보았습니다. 그리고 알파고에서 적용되었던 강화 학습 기법 기반의 AI 솔루션을 도입했습니다. PPA (Power, Performance, and Area) 최적화라 불리는 칩 설계 최적화는 다음과 같은 이유로 바둑 문제와 같습니다. 설계 목표가 주어지면 목표를 만족시키는 전자 회로의 경우의 수가 결정됩니다. 합성을 통해 이 중 한 전자 회로가 산출 되면 해당 프로세서 설계의 타이밍, 성능, 전력 소모 등의 파라미터들이 결정됩니다. 문제는 방대한 Design Space에서 특정 목표를 만족하는 최적의 점을 찾는 것입니다. 이는 알파고의 목표와 같습니다. Synopsys에 따르면 체스의 경우 10의 123승, 바둑의 경우 10의 360승, 칩 설계의 경우 10의 90,000승의 경우의 수가 존재한다고 합니다. 다시 말해 칩 설계 AI의 경우 훨씬 더 많은 경우의 수 내에서 최적해를 찾아야 합니다. Synopsys는 알파고와 같이 강화학습 기법을 기반으로 이 문제를 해결했습니다.

DSO.ai는 인간 전문가에 비해 훨씬 더 적은 시간을 들여 훨씬 더 좋은 결과물을 산출해냈습니다. 전력 소모 절감을 목표로 설정한 경우, DSO.ai는 월드 클래스의 인간 전문가가 약 3개월에 걸쳐 최적화한 칩 설계보다 26% 적은 파워를 소모하는 칩을 설계해 냈습니다. 전력 소모 절감과 성능(타이밍)향상 둘 다를 목표로 설정한 경우에도 DSO.ai는 인간 전문가가 몇 개월에 걸쳐 최적화한 결과보다 더 좋은 칩을 단 몇 주만에 설계해냈습니다. 이러한 결과는 프로세서의 Time-to-market 단축, 제조 비용 절감 등의 효과로 이어집니다.

CAD (Computer-Aided Design)이 처음 도입되었을 때 인간은 컴퓨터’로’ 컴퓨터를 설계할 수 있게 되었습니다. AI의 도입으로 이제는 컴퓨터’가’ 컴퓨터를 설계하는 시대가 도래했습니다. Hotchips 2021에서 Aart CEO는, “AI가 설계 최적화를 넘어 하드웨어 아키텍처를 설계하는 시대를 상상해보라!” 라고 말합니다. 앞으로는 DSO.ai와 같은 기술들로 인해 하드웨어 칩의 설계 및 제조 시간과 원가가 크게 절감될 것입니다. 그렇게 되면 많은 회사들이 각자의 비즈니스에 최적화된 하드웨어 칩과 솔루션을 가지는 미래가 올 수도 있을 것 같습니다. 그때는 CPU나 GPU 등의 범용 프로세서들이 시장에서 고전하지 않을까요?